# TECHNICAL GUIDELINES

Application of Inverters to Mitigate Fault Current Contribution of Inverter-based Distributed Generation in Distribution Systems

2024

Distribution Network Division TENAGA NASIONAL BERHAD

### **TECHNICAL GUIDELINES**

#### APPLICATION OF INVERTERS TO MITIGATE THE FAULT CURRENT CONTRIBUTION OF INVERTER-BASED DISTRIBUTED GENERATION IN DISTRIBUTION SYSTEMS

December 2024

Distribution Network Division Tenaga Nasional Berhad

#### Copyrights

The Technical Guidelines for the Application of Inverters to Mitigate the Fault Current Contribution of Inverter-based Distributed Generation in Distribution Systems are copyrighted by Tenaga Nasional Berhad (TNB) under the Copyright Act of Malaysia. These guidelines are made available by TNB for a wide range of public and private uses, including reference in laws and regulations, as well as private self-regulation, standardisation and promotion of engineering practices and methods. The availability of these guidelines for use and adoption by public authorities and private users does not constitute a waiver of TNB's copyright in the documents.

#### Foreword

In the evolving energy landscape, distribution networks must adapt to the increasing complexity resulting from the integration of renewable energy and advanced technological innovations. The growth of inverter-based distributed generation (DG) presents both opportunities and challenges in ensuring the stability, reliability and security of our distribution systems.

These technical guidelines for the *Application of Inverters* to *Mitigate the Fault Current Contribution of Inverter-Based Distributed Generation in Distribution Systems* address a critical issue: managing the fault current contribution of inverter-based DG to maintain the operational integrity of our networks. As Malaysia accelerates its energy transition, the adoption of such

guidelines is critical to aligning our commitment to sustainability while maintaining the robustness of our distribution networks.

Through a collaborative effort involving experts from TNB Distribution Network Division and TNB Research Sdn. Bhd., these guidelines represent the culmination of rigorous research, practical insights and a forward-looking approach to addressing the challenges posed by inverter-based DG. The recommendations contained herein are designed to assist engineers, planners and technical teams in implementing effective solutions to mitigate fault current contributions, ensure system reliability and optimise grid performance.

As the distribution network becomes more dynamic with the increasing penetration of renewables and distributed generation, the role of technical guidance is essential. By adopting these practices, we can confidently navigate the complexities of grid modernisation while ensuring the reliability and security of electricity supply to our customers.

I encourage all stakeholders, including regulators and industry players, to engage deeply with the principles and recommendations presented in these guidelines. Together, we can drive innovation, enhance operational excellence and support Malaysia's vision for a sustainable energy future.

Thank you.

**Ir. Mahathir Nor bin Ismail** Chief Distribution Network Officer Tenaga Nasional Berhad

#### Acknowledgement

The development of the technical guidelines for the *Application of Inverters to Mitigate the Fault Current Contribution of Inverter-Based Distributed Generation in Distribution Systems* represents a significant step forward in addressing the evolving challenges of modern distribution networks. These guidelines serve not only as a technical reference, but also as a testament to our commitment to fostering innovation, reliability and sustainability within the Distribution Network Division.

This achievement would not have been possible without the collective effort and expertise of an exceptional team. First and foremost, I would like to express my sincere gratitude to the visionary leadership of Tenaga Nasional Berhad and the Distribution Network Division, whose unwavering support

and encouragement have been the cornerstone of this initiative. Their guidance has inspired us to strive for excellence in developing solutions to enhance the resilience and adaptability of our network.

I would like to acknowledge the invaluable contributions of the technical experts and practitioners whose insights and dedication have been instrumental in the development of these guidelines. Special thanks go to Ir. Hamdan bin Ali, Ir. Lim Chia Yih, Ir. Mohd Shukri bin Ismail, Ir. Ts. Musnazril bin Mustaq Khan, Ahmad Farid bin Mohd Perdaus, Ir. Mohd Fahri bin Zamri, Ir. Muhammad Hafizuddin bin Mohamad, Elmi binti Jani, Ir. Mohd Nazmi bin Abdul Raman and Ir. Ts. Mohammad Rhaiz bin Abdul Aziz @ Mohamad and the teams at TNB Research Sdn. Bhd., Ir. Dr Sheikh Kamar bin Sheikh Abdullah, Mohd Khairun Nizam bin Mohd Sarmin, Muhammad Syahir bin Turiman and Dr Farihan binti Mohamad, whose tireless efforts have ensured the quality and relevance of this document. Their collaborative spirit and technical acumen are greatly appreciated.

I would also like to thank the Energy Commission of Malaysia (ST), the Sustainable Energy Development Authority Malaysia (SEDA), the Malaysian Photovoltaic Industry Association (MPIA) and other stakeholders whose feedback and recommendations have enriched the content of these guidelines. Their input has been instrumental in aligning our efforts with regulatory requirements and operational objectives.

Finally, I would like to thank all the teams and individuals involved in the production, review and publication process, from technical drafting to final design and printing. Their dedication and attention to detail have made this vision a reality.

As we look to the future, I am confident that these guidelines will serve as an important tool in mitigating the challenges posed by inverter-based distributed generation and in supporting our journey towards a more sustainable and resilient energy future.

Thank you all for your contributions, hard work and unwavering commitment to excellence!

**Prof. (Adj.) Ir. Ts. Zahari bin Dollah** Head (Asset Management) Distribution Network Tenaga Nasional Berhad

#### Contents

| Fore | word           |                                                                                                 | i         |

|------|----------------|-------------------------------------------------------------------------------------------------|-----------|

| Ackn | owle           | edgement                                                                                        | ii        |

| 1.0  | Defir          | nitions and Acronyms                                                                            | 1         |

| 1.1  | De             | finitions                                                                                       | 1         |

| 1.2  | Acı            | ronyms                                                                                          | 7         |

| 2.0  | Over           | view                                                                                            | 8         |

| 2.1  | Intr           | roduction                                                                                       | 8         |

| 2.2  | Sco            | ope of Guidelines                                                                               | 9         |

| 2.   | .2.1           | Fault Level Mitigation Strategies                                                               | 9         |

| 2.   | .2.2           | Compliance Requirements                                                                         | 9         |

| 2.   | .2.3           | Testing and Evaluation Procedures                                                               | 9         |

| 2.   | .2.4           | Interpretation of Test Results                                                                  | 10        |

| 2.3  | Pu             | rpose                                                                                           | 10        |

| 2.4  | Rig            | pht to Amend Guidelines                                                                         | 10        |

| 3.0  | Impa           | ect of Increased Fault Levels and Mitigation Measures                                           | . 11      |

| 3.1  | Тур            | pes of Fault Currents                                                                           | 11        |

| 3.2  | Fa             | ult Current Contribution from DG                                                                | 12        |

| 3.3  | Imp            | pact of High Fault Current                                                                      | 13        |

| 3.4  | Mit            | igation Measures for Increased Fault Levels                                                     | 14        |

| 3.5  | Inv            | erter Momentary Cessation                                                                       | 14        |

| 4.0  | Regu           | ulatory Framework and Standards                                                                 | . 15      |

| 4.1  | Re             | levant Regulations and Standards                                                                | 15        |

| 4.2  | Co             | mpliance Requirements for Inverters                                                             | 16        |

| 4.   | .2.1           | Short-Circuit Current in Three-Phase A.C. Systems (IEC 60909-0:2016)                            | 16        |

| 4.   | .2.2           | Connection Requirements (Distribution Code: 7.8.3.4)                                            | 16        |

| 4.   | .2.3           | Short-Circuit Levels (Distribution Code: 5.4.9)                                                 | 17        |

| 4.   | .2.4           | Short-Circuit Ratings (ESAH: 1.1.4.5)                                                           | 17        |

| 4.   | .2.5           | Low Voltage Ride-Through (Distribution Code: 6.5.5.1)                                           | 17        |

| 4.   | .2.6           | Low Voltage Ride-Through Performance (IEEE Std 1547-2018: 6.4.2.3.3)                            | 18        |

|      | .2.7<br>1.4.2) | Fault Current Characterisation for Electronically Coupled DER ( <i>IEEE Std 1547-2018</i><br>18 | <i>3:</i> |

| 5.0  | Shor           | t-Circuit Test for Utility-Interconnected Inverters                                             | . 19      |

| 5.1  | Pu             | rpose                                                                                           | 19        |

| 5.2  | Sco            | ope                                                                                             | 19        |

| 5.3  |                | Test Circuit and Equipment                                                                      | 19        |

| 5.3.1      | Test Circuit                                      | 20 |

|------------|---------------------------------------------------|----|

| 5.3.2      | Test Equipment                                    | 20 |

| 5.3.3      | Converter-based Grid Simulator                    | 21 |

| 5.4 Тур    | e Test                                            | 22 |

| 5.4.1      | Test Protocol                                     | 22 |

| 5.4.2      | Test Curve                                        | 24 |

| 5.4.3      | Test Procedure                                    | 24 |

| 5.5 Ass    | essment Criteria                                  | 25 |

| 5.5.1      | Maximum Short-Circuit Current Contribution        | 25 |

| 5.5.2      | Controlled Short-Circuit Current Contribution     | 26 |

| 5.6 Data   | a Requirements                                    |    |

| 6.0 Short  | -Circuit Testing and Certification of Inverters   | 27 |

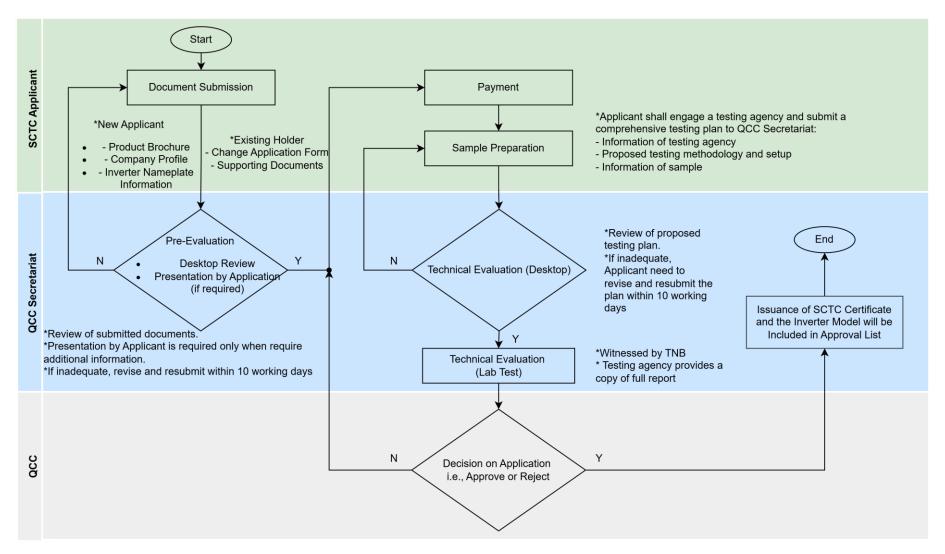

| 6.1 Ove    | erview                                            | 27 |

| 6.2 Тур    | es of Applicants                                  | 27 |

| 6.3 Qua    | ality Certification Committee (QCC)               |    |

| 6.3.1      | Roles and Responsibilities of the QCC Chairman    |    |

| 6.3.2      | Roles and Responsibilities of QCC Members         |    |

| 6.3.3      | Roles and Responsibilities of the QCC Secretariat | 29 |

| 6.4 SCT    | ΓC Terms and Conditions                           | 29 |

| 6.5.1      | Submission of Documents                           |    |

| 6.5.2      | Pre-evaluation                                    |    |

| 6.5.3      | Payment                                           |    |

| 6.5.4      | Sample Preparation                                |    |

| 6.5.5      | Technical Evaluation (Desktop)                    |    |

| 6.5.6      | Technical Evaluation (Laboratory Testing)         |    |

| 6.5.7      | Decision on Application                           | 35 |

| 6.5.8      | Issuance of SCTC Certification                    |    |

| Appendix A | (informative) Bibliography                        | 37 |

| Appendix B | (informative) Sample of Test Report               | 39 |

#### 1.0 Definitions and Acronyms

#### 1.1 Definitions

| Terms         | Definitions                                                        |

|---------------|--------------------------------------------------------------------|

| Act           | The Electricity Supply Act 1990 including                          |

|               | any regulations made hereunder and any                             |

|               | amendments thereto.                                                |

| Apparatus     | Any electrical apparatus and includes the                          |

|               | device or fitting in which a conductor is                          |

|               | used, or of which it forms part of.                                |

| Applicant     | A company or person applying for Short-                            |

|               | Circuit Testing and Certification (SCTC).                          |

| Area EPS      | An EPS/System, also referred to as a                               |

|               | Distribution System that serves Local                              |

|               | EPSs/Embedded Distributor's                                        |

|               | Distribution System.                                               |

| Area EPS      | The entity, also referred to as the                                |

| Operator      | Distribution System Operator (DSO),                                |

|               | responsible for designing, building,                               |

|               | operating, and maintaining the <b>Area</b>                         |

|               | EPS/Distribution System.                                           |

| Certificate   | A company or person who already has                                |

| Holder        | SCTC.                                                              |

| Connection    | An agreement between the                                           |

| Agreement     | Distributor/Embedded Distributor and                               |

|               | any other entity (owner of <b>Transmission</b>                     |

|               | System/Users) setting out the terms                                |

|               | relating to a connection with the relevant                         |

| Connection    | Distribution System.<br>Point of entry or exit of the Distribution |

| Point         | System.                                                            |

| Consumer      | A person who is supplied with electricity or                       |

| (Customer)    | whose premises are for the time being                              |

|               | connected for the purpose of supply of                             |

|               | electricity by a supply authority or <b>Licensee</b>               |

| Consumer With | A <b>Consumer</b> with one or more <b>Generating</b>               |

| Own           | Unit(s) connected to the Consumer's                                |

| Generation    | <b>System</b> , with or without energy storage                     |

|               | system, providing all or part of the                               |

|               | <b>Consumer's</b> electricity requirements, and                    |

|               | which may use the <b>Distributor's</b>                             |

|               | Distribution System or Distribution                                |

|               | System of an Embedded Distributor for                              |

|               | the transport of any surplus of electricity                        |

|               |                                                                    |

| Terms         | Definitions                                                                          |

|---------------|--------------------------------------------------------------------------------------|

| Current       | An inductive coil having a large inductive                                           |

| Limiting      | reactance and is used for limiting Short-                                            |

| Reactor (CLR) | Circuit Currents during fault conditions.                                            |

| DER Operator  | The entity responsible for operating and                                             |

|               | maintaining the <b>DER</b> .                                                         |

| DG Operator   | The entity responsible for operating and                                             |

|               | maintaining the <b>DG</b> .                                                          |

| Distributed   | A source of electric power that is not                                               |

| Energy        | directly connected to a bulk power system.                                           |

| Resources     | DER includes both Generating Units and                                               |

| (DER)         | Energy Storage Systems capable of                                                    |

|               | exporting active power to a <b>Distributor's</b>                                     |

|               | Distribution System.                                                                 |

| Distributed   | A decentralised electricity generation,                                              |

| Generation    | where a Generator, including a Consumer                                              |

| (DG)          | With Own Generation, whose Generating                                                |

|               | Units are directly connected to the                                                  |

|               | Distributor's Distribution System or to                                              |

|               | the <b>Distribution System</b> of an <b>Embedded</b>                                 |

|               | Distributor which is connected to the                                                |

|               | Distributor's Distribution System, and                                               |

|               | not having any connection with the                                                   |

|               | Transmission System.                                                                 |

| Distribution  | A code required to be prepared jointly by                                            |

| Code          | Distributors in Peninsular Malaysia, Sabah                                           |

|               | and F.T Labuan and approved by the                                                   |

|               | commission as revised from time to time                                              |

|               | with the approval of, or by the direction of,                                        |

|               | the commission. It sets out the principles                                           |

|               | governing the relationship between the                                               |

|               | GSO, EC, Customers and all Users of the                                              |

| Distribution  | Distribution System.                                                                 |

|               | The system of electric lines with voltage levels below 66 kV, within the area of     |

| System        | -                                                                                    |

|               | supply owned or operated by the <b>Distributor</b> , for distribution of electricity |

|               | from grid supply points or generating units                                          |

|               | or other entry points to the point of delivery                                       |

|               | to customers or other <b>Distributors</b> and                                        |

|               | includes any electrical plant and meters                                             |

|               | owned or operated by the <b>Distributor</b> in                                       |

|               | connection with the distribution of                                                  |

|               | electricity.                                                                         |

|               | ອເອຍແກບແນ.                                                                           |

| Terms                 | Definitions                                             |

|-----------------------|---------------------------------------------------------|

| Distribution          | Person(s) responsible for the control and               |

| System                | operation of all, or of part of a <b>Distribution</b>   |

| <b>Operator (DSO)</b> | System, or the System of a User which                   |

|                       | operates at Medium Voltage.                             |

| Distributor           | A person who is licensed under Section 9 of             |

|                       | the Act and is connected to the grid system             |

|                       | and distributes electricity for the purpose of          |

|                       | enabling a supply to be given to any                    |

|                       | premises. "Distribute" means to operate,                |

|                       | maintain and distribute electricity through             |

|                       | the electricity distribution network.                   |

| Electric Power        | Facilities that deliver electric power to a             |

| System (EPS)          | load, also referred to as a System.                     |

| Embedded              | A person who distributes electricity under a            |

| Distributor           | Licence issued under the Act and whose                  |

|                       | Distribution System is connected to the                 |

|                       | Distributor's Distribution System under a               |

|                       | Connection Agreement and not having                     |

|                       | any connection with the Transmission                    |

|                       | System; and who is required to comply                   |

|                       | with the <b>Distribution Code</b> as a <b>User</b> at a |

|                       | Connection Point with the Distributor's                 |

|                       | Distribution System and also as a                       |

|                       | Distributor in respect of his own                       |

|                       | Distribution System.                                    |

| Energy Storage        | A device that stores energy to perform                  |

| System                | useful processes at a later time.                       |

| Equipment             | The equipment on which these tests are                  |

| Under Test            | performed and refers to the utility-                    |

| (EUT)                 | interconnected PV inverter.                             |

| Fault Current         | See Short-Circuit current.                              |

| Fault Current         | See Short-Circuit Current Contribution.                 |

| Contribution          |                                                         |

| Fault Current         | A device which limits the prospective Fault             |

| Limiter (FCL)         | Current when a fault occurs without adding              |

|                       | impedance to the circuit during normal                  |

|                       | operation and therefore protecting the grid.            |

| Fault Level           | See Short-Circuit Level.                                |

| Generating Unit       | Any <b>Apparatus</b> that produces electricity.         |

| Generator             | A person who generates electricity under                |

|                       | Licence under the Act.                                  |

| Grid System           | Transmission System with directly                       |

|                       | connected Generating Unit and directly                  |

|                       | connected Customers.                                    |

| Terms                      | Definitions                                                                          |

|----------------------------|--------------------------------------------------------------------------------------|

| Grid System                | Person(s) responsible for the control and                                            |

| Operator (GSO)             | operation of a Transmission System or                                                |

|                            | the System of a User which operates at                                               |

|                            | High Voltage or higher.                                                              |

| Guidelines                 | The Technical Guidelines for the                                                     |

|                            | "Application of Inverters to Mitigate the                                            |

|                            | Fault Current Contribution of Inverter-based                                         |

|                            | Distributed Generation in Distribution                                               |

|                            | Systems"                                                                             |

| High Voltage               | A voltage normally exceeding Medium                                                  |

| (HV)                       | Voltage but equal to or not exceeding                                                |

|                            | 230,000 volts.                                                                       |

| Initial                    | The rms value of the AC symmetrical                                                  |

| Symmetrical                | component of a Prospective Short-Circuit                                             |

| Short-Circuit              | Current, applicable at the instant of Short-                                         |

| Current (I <sub>k</sub> ") | Circuit if the impedance remains at zero-                                            |

|                            | time value.                                                                          |

| Interconnection            | The result of the process of adding <b>DER</b> to                                    |

|                            | an Area EPS/Distributor's Distribution                                               |

|                            | System, whether directly or via                                                      |

|                            | intermediate Local EPS/Embedded                                                      |

|                            | Distributor's Distribution System                                                    |

|                            | facilities.                                                                          |

| Inverter                   | An <b>Apparatus</b> that converts direct current                                     |

|                            | (DC) into alternating current (AC).                                                  |

| Inverter-based             | A <b>DG</b> connected to the grid through a                                          |

| DG                         | power <b>Inverter</b> .                                                              |

| Quality                    | A committee responsible for governing and                                            |

| Certification              | deciding <b>SCTC</b> certification applications.                                     |

| Committee                  |                                                                                      |

| (QCC)<br>Licence           | A licence issued under section 9 of the Act                                          |

| Licence                    |                                                                                      |

|                            | and includes any licence issued under any other law enforced before the promulgation |

|                            | of the Act.                                                                          |

| Licensee                   | A person licensed under section 9 of the                                             |

| FIGENSCC                   | A person licensed under section 9 of the Act.                                        |

| Local Electric             | An <b>EPS/System</b> contained entirely within a                                     |

| Power System               | single premises or group of premises, also                                           |

| (Local EPS)                | referred to as the <b>Distribution System</b> of                                     |

|                            | an <b>Embedded Distributor</b> which is                                              |

|                            | connected to the <b>Distributor's</b>                                                |

|                            | Distribution System.                                                                 |

|                            | Distribution Oystem.                                                                 |

| Terms             | Definitions                                     |

|-------------------|-------------------------------------------------|

| Low Voltage       | A voltage normally exceeding extra low          |

| (LV)              | voltage but not exceeding 1,000 volts           |

|                   | alternating current or 1,500 volts direct       |

|                   | current between conductors, or 600 volts        |

|                   | alternating current or 900 volts direct         |

|                   | current between conductor and earth.            |

| Low Voltage       | The ability of electric generators to remain    |

| Ride-Through      | connected during short periods of lower         |

| (LVRT)            | electric network voltage.                       |

| Medium            | A voltage normally exceeding Low Voltage        |

| Voltage (MV)      | but equal to or not exceeding 50,000 volts.     |

| Momentary         | A temporarily cease to energise an Electric     |

| Cessation         | Power System in response to a                   |

|                   | disturbance of the applicable voltages or       |

|                   | the system frequency, with the capability of    |

|                   | immediate restore output of operation when      |

|                   | the applicable voltages or the system           |

|                   | frequency return to within defined ranges.      |

| National          | Malaysia's comprehensive strategic plan to      |

| Energy            | steer the energy systems away from              |

| Transition        | conventional, fossil fuel-based sources and     |

| Roadmap           | towards cleaner, more sustainable               |

| (NETR)            | alternatives.                                   |

| Peak Short-       | The maximum possible instantaneous value        |

| Circuit Current   | of the Prospective Short-Circuit Current.       |

| (l <sub>p</sub> ) |                                                 |

| Prospective       | The current that would flow if the Short-       |

| Short-Circuit     | Circuit were replaced by an ideal               |

| Current           | connection of negligible impedance without      |

|                   | any change of the supply.                       |

| PV Simulator      | A simulator that has I-V characteristics        |

|                   | equivalent to a PV array.                       |

| Short-Circuit     | An accidental or intentional conductive path    |

|                   | between two or more conductive parts            |

|                   | forcing the electric potential differences      |

|                   | between these conductive parts to be equal      |

| Chart Olar It     | or close to zero.                               |

| Short-Circuit     | An over-current resulting from a <b>Short</b> - |

| Current           | <b>Circuit</b> in an electric system.           |

| Short-Circuit     | A short-circuit current contribution from       |

| Current           | machines, devices or systems, such as           |

| Contribution      | Inverters.                                      |

| Short-Circuit     | The amount of current that flows on the         |

| Level             | system during a fault.                          |

| Terms                     | Definitions                                       |

|---------------------------|---------------------------------------------------|

| Short-Circuit             | A series of in-depth evaluations of the           |

| Testing and               | Short-Circuit Current Contribution of             |

| Certification             | Inverters to be integrated into the               |

| (SCTC)                    | Distribution System.                              |

| Steady-State              | The rms value of the Short-Circuit Current        |

| Short-Circuit             | which remains after the decay of the              |

| Current (I <sub>k</sub> ) | transient phenomena.                              |

| Suruhanjaya               | The Energy Commission (EC) established            |

| Tenaga (ST)               | under the Energy Commission Act 2001.             |

| Sustainable               | A statutory body formed under the                 |

| Energy                    | Sustainable Energy Development Authority          |

| Development               | Act 2011 [Act 726].                               |

| Authority                 |                                                   |

| (SEDA)                    |                                                   |

| Symmetrical               | The rms value of the AC symmetrical               |

| Short-Circuit             | component of a <b>Prospective Short-Circuit</b>   |

| Current                   | Current, the aperiodic component of               |

|                           | current, if any, being neglected.                 |

| System                    | An electrical system in which all conductors      |

| -                         | and equipment are electrically or                 |

|                           | magnetically connected.                           |

| Technical                 | The testing and evaluation of                     |

| Evaluation                | manufacturer's test product for compliance        |

|                           | with specification, quality, and suitability in   |

|                           | accordance with the process and dates             |

|                           | outlined in the Guidelines.                       |

| Technical                 | Person(s) from the Quality Assurance Unit,        |

| Evaluator                 | TNB Labs, responsible for conducting the          |

|                           | Technical Evaluation.                             |

| Tenaga                    | A Licensee that was issued a Licence on           |

| Nasional                  | 1st September 1990 which authorises <b>TNB</b>    |

| Berhad (TNB)              | to own and operate electricity generating,        |

|                           | transmitting and distributing facilities and to   |

|                           | supply energy to other persons therefrom.         |

| Testing Agency            | The test and verification authority               |

|                           | responsible for performing type tests and         |

|                           | overseeing production testing programs to         |

|                           | verify conformance of the <b>DER</b> to the       |

|                           | standard.                                         |

| TNB                       | The Distribution Network Division of <b>TNB</b> . |

| Distribution              |                                                   |

| Network (DN)              |                                                   |

| TNB Labs                  | A wholly-owned subsidiary of TNB                  |

|                           | Research, a leading provider of quality           |

|                           | assurance, scientific services, technical         |

|                           | services and advanced diagnostic services.        |

|                           | <b>5</b>                                          |

| Terms        | Definitions                                  |

|--------------|----------------------------------------------|

| Transmission | The system of electric lines with voltage    |

| System       | levels at or above 66 kV owned or operated   |

|              | by the transmission system Licensee.         |

| Type Test    | A test of one or more devices manufactured   |

|              | to a certain design to demonstrate, or       |

|              | provide information that can be used to      |

|              | verify, that the design meets the            |

|              | requirements specified in these              |

|              | Guidelines.                                  |

| User         | A term used in various sections of the       |

|              | Distribution Code to refer to the persons    |

|              | using the Distributor's Distribution         |

|              | System, more particularly identified in each |

|              | section of the Distribution Code, but        |

|              | excluding the Transmission System            |

|              | Licensee or Grid System Operator.            |

| 1.2 Acronyms | A/D<br>AC<br>COMTRADE<br>CSV<br>DC<br>DG<br>GW<br>IEC<br>IEEE<br>kA<br>kV<br>LSS<br>NEM<br>PDF<br>PQIF<br>PV | Analogue-to-Digital<br>Alternating current<br>Common format for Transient Data Exchange<br>for power systems<br>Comma-Separated Values<br>Direct current<br>Distributed generation<br>Gigawatts<br>International Electrotechnical Commission<br>Institute of Electrical and Electronics Engineers<br>kiloampere<br>kilovolt<br>Large-scale solar<br>Net Energy Metering<br>Portable Document Format<br>Power Quality Data Interchange Format<br>Photovoltaic |

|--------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|              | RE                                                                                                           | Renewable energy                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | rms                                                                                                          | Root mean square                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### 2.0 Overview

2.1 Introduction The Malaysian government has taken a substantial step towards addressing climate change and achieving its net-zero emissions target by 2050. In a recent announcement, the government released the **National Energy Transition Roadmap (NETR)** [3], which provides a comprehensive plan outlining the various measures to be implemented. The objective of these measures is to facilitate a transition in the country's energy sector towards the utilisation of cleaner and more sustainable sources.

A significant aspect of the roadmap is the prioritisation of renewable energy (RE). The government has revised its target for installed RE capacity, raising it from the current target of 40% by 2040 to an ambitious 70% by 2050. It is anticipated that this heightened ambition will be largely driven by the installation of solar photovoltaic (PV) systems. In order to achieve this objective, it will be necessary to witness a considerable expansion in solar capacity over the course of the next three decades, with a projected target of 59 GW of installed capacity by 2050.

As **Distribution Systems** evolve to accommodate the increasing penetration of renewable energy systems, a critical challenge is the management of **Fault Currents**. **Fault Currents**, which result from **Short Circuits** or other disturbances in the network, can present risks to the reliability of the system, the integrity of the equipment and the safety of personnel. The efficacy of conventional **Fault Level** management techniques, such as the utilisation of fixed impedance devices, such as **Current Limiting Reactors (CLRs)**, may be compromised or rendered impractical in the context of evolving network dynamics.

In response to these challenges, the deployment of **Inverters** represents a promising solution to mitigate the increasing **Fault Level** resulting from the integration of **Inverter-based Distributed Generation (DG)** into the **Distribution System**. **Inverters** offer the potential to actively control their **Fault Current Contribution** and thus reduce the stress on the grid during fault events.

In light of the aforementioned feature, **TNB** is putting forth a novel proposition for prospective **DG Operators**, with the objective of mitigating the anticipated **Short-Circuit Current Contributions** from solar **Inverters** in areas characterised by high **Fault Levels**. However, in order to realise the full potential of **Inverters** for **Fault Level** mitigation, it is first necessary to gain a comprehensive understanding of their performance characteristics and operational capabilities.

- 2.2 Scope of Guidelines The Guidelines focus on the management of Fault Levels through Inverter applications for the integration of Inverter-based DGs with a capacity of more than 425kW into existing high Fault Level areas in the Distribution System. It places particular emphasis on adherence to standards, comprehensive test procedures and the interpretation of results, with specific reference to maximum Short-Circuit Current Contribution and controlled Short-Circuit Current Contribution.

- 2.2.1 Fault Level The Guidelines address the increase in Fault Levels due to the integration of Inverter-based DG into the Distribution System. This is achieved by utilising the capabilities of Inverters through current limiting techniques, which serve to reduce the Inverter Short-Circuit Current Contribution.

- 2.2.2 Compliance The **Guidelines** address compliance with relevant regulatory standards and industry specifications for the integration and operation of **Inverters** in **Distribution Systems**.

- 2.2.3 Testing and Evaluation Procedures The **Guidelines** set forth comprehensive procedures for assessing the maximum **Short-Circuit Current Contribution** of **Inverters** and their ability to control **Short-Circuit Currents** during fault events. This includes the configuration of the test setup, the instrumentation required, the data collation, the methodologies used in the data analysis, and the format of the resulting report.

This type test is mandatory for **DG Operators** opting to mitigate **Fault Levels** using **Inverters** for **Inverter-based DGs** with a capacity greater than 425kW in existing high **Fault Level** areas of the **Distribution System**.

- 2.2.4 Interpretation of Test Results The **Guidelines** provide guidance on the interpretation and analysis of test results obtained from **Inverter Short-Circuit** tests, including assessment of maximum **Short-Circuit Current Contribution**, and controlled **Short-Circuit Current Contribution**.

- 2.3 Purpose The purpose of these **Guidelines** is to establish a systematic framework for the assessment and implementation of mitigation strategies utilising **Inverters** in response to the rising **Fault Level** resulting from the integration of **Inverter-based DG** into **Distribution Systems**. The objective of these **Guidelines** is to facilitate the integration of **Inverter** technologies into **Distribution Systems** while ensuring safety, reliability and compliance with regulatory requirements. This will be achieved by establishing standardised test procedures and best practices.

- 2.4 Right to Amend Guidelines **TNB** reserves the exclusive right to amend, modify or revise any clause, requirement or provision of these **Guidelines** at its sole discretion without prior notice to any party. It is the **Applicant's** responsibility to ensure compliance with the latest version of the **Guidelines**. By submitting an application or continuing to comply with the requirements set forth herein, the **Applicant** acknowledges and agrees to comply with any updates or changes made by **TNB**.

#### 3.0 Impact of Increased Fault Levels and Mitigation Measures

3.1 Types of Fault Currents

Protection systems are an essential component of the design and operation of power systems. Their primary function is to detect anomalies between phases or between phases and the ground. The formation of accidental conduction paths results in a Short-Circuit phenomenon, whereas the blocking of current gives rise to an open-circuit phenomenon. In the majority of instances, Short-Circuit faults are more prevalent; thus, the term "fault" is typically employed to denote a Short-Circuit [4].

> The occurrence of a **Short-Circuit** is contingent upon the contact of energised electrical components at different voltages. This results in a reduction of impedance between nodes to a near zero value, thereby redirecting the current from its intended path. **Short circuits** have the potential to release currents that are orders of magnitude larger than the normal operating current, which can result in the generation of heat and magnetic force, as well as damage to equipment and endanger safety.

> The most common causes of faults in **Distribution Systems** are insulation breakdown, mechanical issues and thermal issues [5]. Insulation breakdown is caused by system overvoltage, which can result from lightning strikes and switching surges, as well as from improper fabrication or installation, or from the ageing or contamination of the insulation. Mechanical issues may be caused by contact with animals or trees, vehicle collisions, or natural disasters. Thermal issues may arise as a consequence of overcurrent or overvoltage conditions.

> Faults can be classified into two main categories: symmetrical and asymmetrical. Symmetrical faults, defined as three-phase faults, result in balanced fault conditions, frequently accompanied by the occurrence of high **Fault Currents**. Asymmetrical faults occur when the current flow between phases is unbalanced, resulting in the generation of currents with different magnitudes and phase angles. Examples of asymmetrical faults include line-to-line, line-to-ground and double line-to-ground faults.

Distribution substations are designed to withstand **Short-Circuit Currents**. However, it is not possible to completely eliminate **Short Circuits**. Instead, the goal is to detect and clear the fault quickly while minimising its impact. 3.2 Fault Current Contribution from DG The contribution of **DGs** to **Fault Currents** is dependent on the specific type of **DG**, which can be broadly classified as synchronous generators, induction generators, and **Inverter**based units. However, the response of each type to a fault and its contribution to the **Fault Current** may vary.

The contribution of **Inverter-based DGs** to **Fault Current** has been demonstrated to be no greater than 200% of their rated current in a number of studies [6]-[10]. The **Fault Current Contribution** of different types of **DG** can be summarised in Table 3-1.

Table 3-1. Estimation of **Fault Current Contributions** for different types of **DGs** [11].

| Type of DGs                                              | Fault Current Contributions                                                                                                                                      |

|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inverter-based                                           | 1-2 times the <b>Inverter</b> rated<br>current, with a duration spanning<br>from a half cycle to several<br>cycles, depending on the control<br>method employed. |

| Synchronous generator<br>with separate exciter<br>source | 5-10 times the generator rated<br>current in sub-transient and<br>transient cycles, 2-4 times the<br>generator rated current in<br>steady-state condition.       |

| Inductor generator or self-<br>excited generator         | 5-10 times the generator rated current in the first few cycles, negligible after 5-10 cycles.                                                                    |

Furthermore, the influence of **DGs** on **Fault Level** is also contingent upon the following factors [12]:

- The distance of the **DG** from the fault, as the increased cable impedance over longer distances will reduce the **Fault Current**.

- Whether or not there is a transformer between the fault location and the contributing **DG** (which is often the case for voltage regulation purposes), as the **Short-Circuit** impedance of the transformer can help to limit the **Fault Current**.

- The configuration of the network between the **DG** and the fault, as different paths for the flow of the **Fault Current** will alter the magnitude of the **Fault Current** (due to cable impedances and other installed equipment).

- The method of coupling the **DG** to the network. Directly connected **DGs** will contribute significantly higher **Fault Currents** than **DGs** connected via power electronic interfaces.

- 3.3 Impact of High Fault Current

The increasing prevalence of DGs in Distribution Systems has been observed to correlate with an increase in Short-Circuit Currents, which can exacerbate the severity of downstream faults [13]. Although a single DG may not have a considerable impact on Fault Currents, the collective effect of multiple DG connections can significantly disrupt Fault Current levels and protection systems. [14].

The occurrence of high **Fault Currents** can result in thermal stress within power system equipment, due to the resistive heating that ensues as a consequence of the increased current flow. Such a sudden rise in temperature has the potential to accelerate the deterioration of the insulation materials used in these components. To illustrate, in a transformer, an elevated temperature results in accelerated deterioration of the insulating materials situated between the windings. This deterioration diminishes the dielectric strength and heightens the probability of insulation failure.

Similarly, power cables are susceptible to thermal damage to their insulation, which reduces the insulation resistance and increases the likelihood of faults. Even circuit breakers, which are designed to interrupt **Fault Currents**, are not immune to thermal stress on their contacts due to arcing during fault clearance [15].

Furthermore, high fault contributions from **DGs** can render some relays to be blinded [16]. Changes in the **Fault Levels** within the power system can affect the operation of protection devices. The integration of the **DG** would have negative impacts on these devices, including [14]:

- Reverse power flow

- False tripping

- Blinding of protection

- Unintentional islanding

- Unsynchronised reclosing

- Loss of main supply

| 3.4 | Mitigation<br>Measures for<br>Increased Fault<br>Levels | Clause 5.4.9 of the <b>Distribution Code</b> stipulates that the <b>DG</b><br><b>Operator</b> is obliged to minimise its <b>Fault Current</b> contribution in<br>response to a reasonable request from the <b>Distributor</b> . Mitigation<br>measures for increased <b>Fault Levels</b> include the introduction of<br>higher impedances, such as the utilisation of <b>Current Limiting</b><br><b>Reactors (CLRs)</b> or transformers with higher short-circuit<br>impedance. These measures serve to restrict the magnitude of<br><b>Fault Currents</b> . However, this may result in an increase in network<br>losses and the necessity for maintaining the voltage profile.<br>Conversely, <b>Fault Current Limiters (FCLs)</b> are capable of<br>detecting the rapid rise in <b>Fault Current</b> and injecting a<br>pyrotechnic charge to open the main current path. Nevertheless,<br>this necessitates the replacement of contacts and fuses following<br>each operation. |

|-----|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.5 | Inverter<br>Momentary                                   | <b>Momentary Cessation</b> , also referred to as "blocking", is defined<br>as the phenomenon of no current being injected into the grid by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Inverter Momentary Cessation, also referred to as "blocking", is defined Momentary as the phenomenon of no current being injected into the grid by Cessation the Inverter during low or high voltage conditions that fall outside of the continuous operating range. The phenomenon of Momentary Cessation can be attributed to the blocking of power electronic firing commands, which in turn prevents the Inverter from generating active or reactive current (and, consequently, no active or reactive power) [17].

#### 4.0 Regulatory Framework and Standards

4.1 Relevant Regulations and Standards The effective implementation of **Inverter** applications to mitigate increased **Fault Levels** in the **Distribution System** necessitates compliance with the various regulations and standards set forth by regulatory authorities and industry organisations. These regulations and standards, enumerated in Table 4-1, provide guidelines and requirements for the deployment and operation of **Inverter** technology in the **Distribution System**.

Table 4-1. Regulations and standards relevant to the integration of **Inverter**.

| No. | Regulation       | Standards & Guidelines                              |

|-----|------------------|-----------------------------------------------------|

| 1.  | Suruhanjaya      | Distribution Code for Peninsular                    |

|     | Tenaga (ST)      | Malaysia, Sabah & F.T. Labuan                       |

| 2.  | Suruhanjaya      | Guidelines on Large Scale Solar                     |

|     | Tenaga (ST)      | Photovoltaic Plant for Connection to                |

|     |                  | Electricity Networks                                |

| 3.  | Suruhanjaya      | Guidelines for Solar Photovoltaic                   |

|     | Tenaga (ST)      | Installation Under the Programme of                 |

|     |                  | NEM Rakyat and NEM GoMEn in                         |

|     |                  | Peninsular Malaysia                                 |

| 4.  | Suruhanjaya      | Guidelines on the Connection of                     |

|     | Tenaga (ST)      | Solar Photovoltaic Installation for                 |

|     |                  | Self-Consumption                                    |

| 5.  | Tenaga Nasional  | Electricity Supply Application                      |

|     | Berhad (TNB)     | Handbook (ESAH)                                     |

| 6.  | Tenaga Nasional  | Technical Guidelines for                            |

|     | Berhad (TNB)     | Interconnection of Distributed                      |

|     |                  | Generator to Distribution System                    |

| 7.  | Tenaga Nasional  | Technical Guideline for Connection                  |

|     | Berhad (TNB)     | of Indirect Solar PV Power                          |

|     |                  | Generation for Net Energy Metering                  |

|     |                  | (NEM 3.0)                                           |

| 8.  | International    | IEC 60909-0: 2016: Short-circuit                    |

|     | Electrotechnical | currents in three-phase a.c. systems                |

|     | Commission (IEC) | <ul> <li>Part 0: Calculation of currents</li> </ul> |

| 9.  | Institute of     | IEEE Std 1547-2018: IEEE Standard                   |

|     | Electrical and   | for Interconnection and                             |

|     | Electronics      | Interoperability of Distributed Energy              |

|     | Engineers (IEEE) | Resources with Associated Electric                  |

|     |                  | Power Systems Interfaces                            |

- 4.2 Compliance Requirements for Inverters Compliance with the various regulatory requirements and industry standards ensures that **Inverters** meet the specified performance criteria and safety standards, thereby enabling them to be seamlessly integrated and operated within **Distribution Systems**.

- 4.2.1 Short-Circuit Current in Three-Phase A.C. Systems (*IEC 60909-0:2016*)

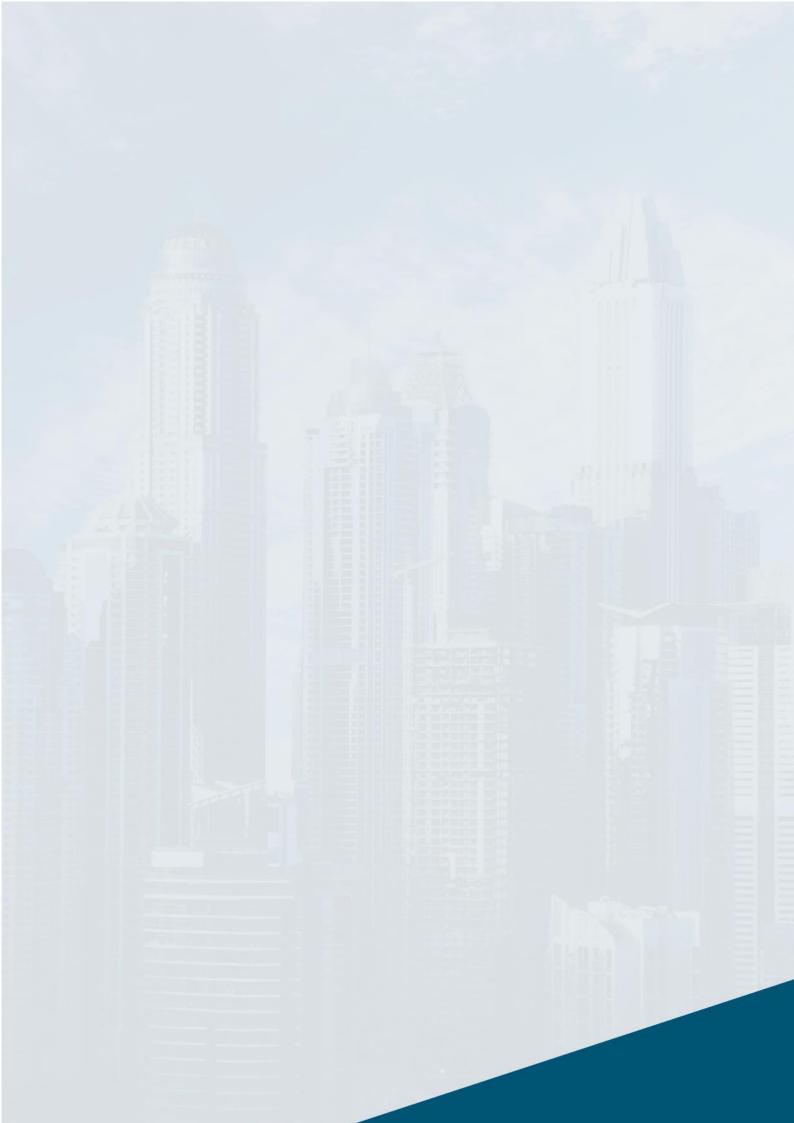

A complete calculation of **Short-Circuit Currents** should yield a representation of the currents as a function of time at the location of the **Short-Circuit**, from the inception of the **Short-Circuit** until its end. This representation should correspond to the instantaneous voltage value at the outset of the **Short-Circuit** (see Figure 4-1).

Figure 4-1. Short-Circuit Current with constant AC component.

- *I*<sub>p</sub> is **Peak Short-Circuit Current**

- *I*<sup>*k*</sup> is **Initial Symmetrical Short-Circuit Current**

- *I*k is **Steady-State Short-Circuit Current**

- *i*<sub>DC</sub> is decaying (aperiodic) component of **Short-Circuit Current** or DC component

- A is initial value of the DC component  $i_{DC}$

- 4.2.2 Connection Requirements (*Distribution Code: 7.8.3.4*)

The generation must comply with the planning and criteria specified in section 5.4 of the Distribution Planning Code and the operation criteria specified in section 6.5 of the Distribution Operating Code, as well as the standard practices on the **Distributor's Distribution System**. The **TNB** and **SEDA** technical guides provide guidance on planning and design. The **Distributor** and the customer must agree in writing on the particular technical requirements for connection, including **Fault** Level.

# 4.2.3 Short-Circuit Levels (Distribution Code: 5.4.9) The Distribution System must be designed to withstand the maximum sub-transient three-phase symmetrical Short-Circuit Fault Levels without exceeding 90% of the switchgear's Short-Circuit breaking and making capacity. Furthermore, the short-time current rating of the connected equipment must be within 90% of the Short-Circuit Current rating of the Distribution System.

**Short-Circuit Levels** must be calculated in accordance with IEC 60909, taking into account the contribution of generating units and motors to the **Short-Circuit Levels**.

The **DG Operator** must provide the **Distributor** with details of the design **Short-Circuit Level** and the actual prospective maximum upon request. The **DG Operator** must also minimise its **Fault Current Contribution** on reasonable request from the **Distributor**.

| 4.2.4 | Short-Circuit  | All equipment proposed for installation and connection to TNB |

|-------|----------------|---------------------------------------------------------------|

|       | Ratings (ESAH: | supply must comply with the following Short-Circuit ratings:  |

|       | 1.1.4.5)       |                                                               |

Table 4-2. Equipment **Short-Circuit** ratings.

| System    | Short-Circuit Rating          |

|-----------|-------------------------------|

| 500 kV    | 50 kA, 1s                     |

| 275 kV    | 40 kA, 3s for bulk station    |

|           | (50kA , 1s for Power          |

|           | Substation and 275kV within   |

|           | 500kV substation)             |

| 132 kV    | 31.5 kA, 3s                   |

|           | (40kA, 3s for substation      |

|           | adjacent to Power Station, or |

|           | within 500/275kV substation)  |

| 33 kV     | 25 kA, 3s                     |

| 22 kV     | 20 kA, 3s                     |

| 11 kV     | 20 kA, 3s                     |

| 6.6 kV    | 20 kA, 3s                     |

| 400/230 V | 31.5 kA, 3s                   |

4.2.5 Low Voltage Ride-Through (*Distribution Code: 6.5.5.1*)

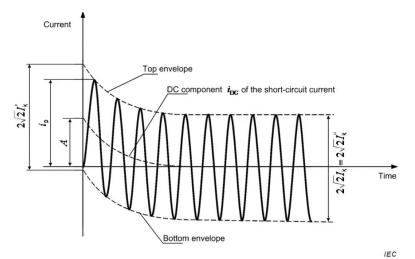

In the event of a disturbance in the transmission system, the **Distribution System** may experience a temporary low voltage or sag. The LSS plant must maintain continuous operation even during fluctuations in the **Distribution System** voltage, as the LVRT curve requirements shown in Figure 4-2.

Figure 4-2. LVRT curve requirements in Distribution System.

- 4.2.6 Low Voltage Ride-Through Performance (*IEEE Std 1547-*2018: 6.4.2.3.3) For Category III **DER**<sup>1</sup>, during temporary voltage disturbances, for which the applicable voltage on the phase that has the least voltage magnitude is within the **Momentary Cessation** operation region, the **DER**

- Shall not trip.

- Shall cease to energise.

- Shall restore output as specified in 6.4.2.7 of IEEE Std 1547-2018.

- 4.2.7 Fault Current Characterisation for Electronically Coupled DER (*IEEE Std 1547-*2018: 11.4.2)

The objective of Fault Current characterisation is to determine the controller response of the DER under certain fault conditions.

The DER Operator must provide the Distribution System Operator<sup>2</sup> with oscillographic voltage and current data for all three phases measured during Type Testing. The sequence impedance characteristics of the external source used during the DER Type Tests must be provided. The DER must be type tested for maximum Short-Circuit Current levels.

<sup>&</sup>lt;sup>1</sup> IEEE 1547-2018 Category III compliant **Inverters** that are required to use **Momentary Cessation** in specific circumstances.

<sup>&</sup>lt;sup>2</sup> Distribution System Operator refers to Area EPS Operator in IEEE Std 1547-2018.

#### **5.0 Short-Circuit Test for Utility-Interconnected Inverters**

5.1 Purpose These requirements are in place to ensure that the **Inverter-based DG** responds as intended to **Short-Circuit** faults in the **Distribution System** in accordance with the technical specifications of IEC TS 62910-2020 [1], and the test procedures of IEEE Std 1547.1-2020 [2]. The fault response characterisation of the device must be performed using the test procedures specified in this subsection.

5.2 Scope These requirements set out a definitive test procedure for evaluating the Short-Circuit Currents of utility-connected Inverters, including direct and indirect connections. These procedures are primarily intended for large-scale systems where Inverters are connected to utility Medium Voltage (MV) Distribution Systems. However, these requirements can also be applied to Low Voltage (LV) installations in areas where there is a requirement to mitigate increased Fault Levels.

The assessment of the **Short-Circuit Current** performance is specific to the configuration and mode of operation of the **Inverter** under test. The **Inverter** must be assessed in each of its factory or user-defined configurations, as variations can affect their **Short-Circuit Current** performance. The measurement procedures are designed to be universally applicable. This ensures that the **Short-Circuit Current** characteristics observed at one test site remain applicable to all other sites.

## 5.3 Test Circuit and The circuits and equipment described in this subsection are developed to allow tests that simulate the full range of anticipated grid faults, including:

- Single phase to ground fault (any phase).

- Two phase isolated fault, between any two phases.

- Two phase grounded fault, involving any two phases.

- Three phase Short-Circuit fault.

A full discussion of these faults may be found in Annex A of IEC TS 62910-2020.

The grid simulator described in 5.3.3 is informative examples and are not intended to restrict design flexibility. Other designs may be used to achieve equivalent test functionality.

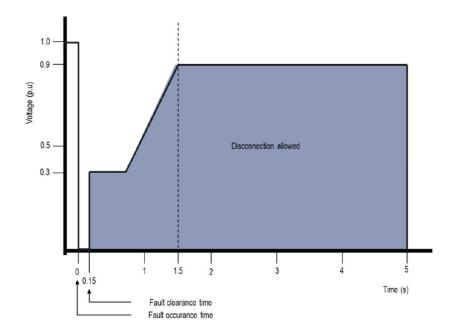

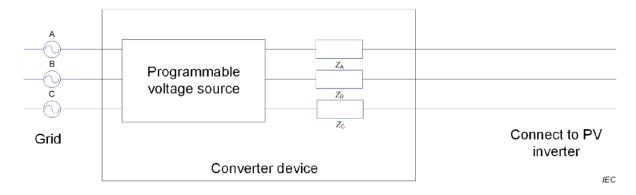

5.3.1 Test Circuit The test circuit comprises a DC source, the **EUT**, a grid fault simulator, and the grid. A **PV Simulator** (or PV array) provides input energy for the **EUT**. The output of the **EUT** is connected to the grid via a grid fault simulator, as shown in Figure 5-1.

Figure 5-1. Testing circuit diagram.

**NOTE** MP1 is the measurement point between the grid and the grid fault simulator; MP2 is the measurement point at the high voltage side of the transformer (optional); MP3 is the measurement point at the **Low Voltage** side of the transformer.

5.3.2 Test Equipment The test equipment shall be as specified in this subsection.

5.3.2.1 Measuring Instruments The waveforms shall be measured using a device with a memory function, such as a storage or digital oscilloscope or a high-speed data acquisition system. The oscilloscope or data acquisition system shall have an accuracy of at least 0.2% of full scale. The measuring instrument's analogue-to-digital (A/D) converter shall have a resolution of at least 12 bits to maintain the required measurement accuracy.

Voltage and current transformers are the sensors required for measurement. The transducers shall have an accuracy of 0.5% of full scale or better. It is necessary to select the transducer measuring range based on the normal value of the signal to be measured. The selected measuring range shall not exceed 150% of the normal value of the measured signal. Table 5-1 sets out the transducer accuracy requirements.

Table 5-1. Accuracy of measurements.

| Measurement Device      | Accuracy        |

|-------------------------|-----------------|

| Data acquisition device | 0.2% full scale |

| Voltage transformer     | 0.5% full scale |

| Current transformer     | 0.5% full scale |

5.3.2.2 DC source A PV array, PV array simulator or controlled DC source with PV characteristics may be used as the DC power source to supply input energy for the **Short-Circuit** test. The DC power source used as the input source for the **EUT** shall be capable of supplying the maximum input power to the **EUT** and other power levels during the test, at the minimum and maximum input operating voltages of the **EUT**.

The **PV Simulator** shall emulate the current/voltage characteristics of the PV module or PV array for which the **EUT** is designed. A **PV Simulator** should have a response time that is no longer than the MPP tracking response time of the **EUT**.

In the case of an **EUT** without galvanic isolation between the DC and AC side, the output of the **PV Simulator** should not be earthed.

The equivalent capacitance between the **PV Simulator** output and the earth should be as low as possible to minimise the impact on the **EUT**.

A PV array used as the **EUT** input source should be capable of matching the **EUT** input power levels specified by the test conditions. The test period should be selected to ensure that the solar irradiance remains stable and does not vary by more than 5% throughout.

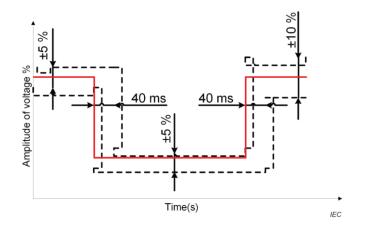

5.3.3 Converterbased Grid Simulator The test circuit utilising a back-to-back converter is shown in Figure 5-2. The test circuit is comprised of a voltage source with low internal resistance, which can be combined with broadband amplifiers (linear or forced switching type) capable of faithfully reproducing three sinusoidal voltages with controlled harmonic content and adjustable amplitude, fundamental frequency, and phase relationship within broad margins.

The converter shall meet the following requirements when used:

- It shall be capable of independently controlling the amplitude and phase angle of the three phases.

- It shall incorporate impedances ZA, ZB, and ZC, which can be adjusted to reproduce the ohmic and inductive components of the **Short-Circuit** impedances typical of the grid.

- It shall be capable of reproducing the phase voltages and relative phase angles occurring on the LV side of the transformers in the event of each of the various fault types.

Figure 5-2. Converter device example.

In the event that the programmable voltage source is of the bidirectional, controlled output voltage type and is capable of replicating the influence of **Short-Circuit** impedances that are typical of the grid, it may be possible to omit the impedances ZA, ZB, and ZC.

5.4 Type Test The tests to characterise the **Inverter-based DG** response to **Short-Circuit** faults on the **Distribution System** must be carried out in accordance with the requirements set out in this subsection.

5.4.1 Test Protocol

The **Short-Circuit** test protocol is designed to verify that the **EUT** responds appropriately to voltage drops (due to grid faults). The **EUT** must demonstrate that it can:

- Appropriately detect the simulated fault.

- Ride through the event and continue operation as specified in the applicable curves.

- Not suffer any damage from the event.

The response to the voltage drop specified in Table 5-2 shall be recorded over the **EUT** operating period with two ranges of output:

- a) part load (between 0.1 Pn and 0.3 Pn);

- b) full load (above 0.9 Pn);

and with two fault conditions:

- c) three-phase drop;

- d) two-phase drop or single-phase drop.

The tests should be carried out at least twice at each test point listed in Table 5-2.

| Drop Depth <sup>a</sup>                                                                     | Minimum<br>Duration <sup>b</sup> | Drop Phase <sup>c</sup> | EUT output conditions <sup>d</sup>           |

|---------------------------------------------------------------------------------------------|----------------------------------|-------------------------|----------------------------------------------|

|                                                                                             |                                  | Three-phase             | Full load (above 0.9 Pn)                     |

|                                                                                             |                                  |                         | Part load (0.1 Pn and 0.3 Pn)                |

|                                                                                             |                                  | Turnahara               | Full load (above 0.9 Pn)                     |

| 0%                                                                                          | 0.15 seconds                     | Two-phase               | Part load (0.1 Pn and 0.3 Pn)                |

| 0%                                                                                          |                                  | Two-phase to ground     | Full load (above 0.9 Pn)                     |

|                                                                                             |                                  |                         | Part load (0.1 Pn and 0.3 Pn)                |

|                                                                                             |                                  | Single-phase to         | Full load (above 0.9 Pn)                     |

|                                                                                             |                                  | ground                  | Part load (0.1 Pn and 0.3 Pn)                |

|                                                                                             |                                  | Three phase             | Full load (above 0.9 Pn)                     |